Những khiếm khuyết nhỏ hơn sợi tóc, cái giá có thể là cả chiếc xe

Một vết nứt hay lỗ rỗng bên trong chip bán dẫn có thể nhỏ hơn đường kính một sợi tóc người, nhưng hậu quả thì hoàn toàn không nhỏ:

- Hệ thống lái trợ lực trên ô tô có thể đột ngột “đơ”,

- Laptop trở nên dễ bị tấn công hơn vì một mạch bảo mật hoạt động chập chờn,

- Cả dây chuyền sản xuất chip trị giá hàng tỉ đô la phải tạm dừng để truy tìm nguồn gốc lỗi.

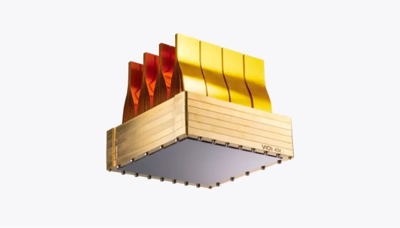

Những lỗi siêu nhỏ này nhiều khi ẩn sâu bên trong cấu trúc đóng gói (packaging) – nơi nhiều chip nhỏ được nối kết điện với nhau trong một module duy nhất. Khi xu hướng advanced packaging ngày càng bùng nổ (chiplet, 2.5D, 3D stacking…), việc tìm và hiểu các khuyết tật trong khối “lego silicon” phức tạp đó trở thành vấn đề sống còn.

Đó là bối cảnh mà Nikhilesh Chawla, Ransburg Professor ngành Khoa học Vật liệu tại Purdue, cùng đồng nghiệp trong trường và các nhà khoa học tại Argonne National Laboratory (thuộc Bộ Năng lượng Mỹ – DOE) đang xây dựng một cách tiếp cận mới kết hợp X‑ray 3D độ phân giải cực cao + thuật toán AI để:

- Soi từng chi tiết siêu nhỏ bên trong chip,

- Làm điều đó không phá hủy linh kiện,

- Và quan trọng nhất: nhanh hơn nhiều so với cách kiểm tra truyền thống.

Tại sao ngành chip cần một “cặp mắt mới”?

Hiện tại, cách xử lý một linh kiện nghi có vấn đề trong nhiều nhà máy là:

- Cắt – mài – mổ linh kiện ra để xem bên trong:

- Dùng cưa, mài, đánh bóng,

- Chụp hiển vi điện tử,

- Phân tích từng lớp.

- Cách này có ba nhược điểm cực lớn:

- Tốn thời gian và công sức,

- Phá hủy hoàn toàn linh kiện, không thể dùng lại,

- Khó tích hợp vào quy trình kiểm tra inline trong dây chuyền sản xuất.

Trong bối cảnh mỗi thế hệ chip mới lại:

- Nhỏ hơn, phức tạp hơn,

- Nhiều lớp đóng gói hơn,

- Và được sản xuất với sản lượng khổng lồ, việc phụ thuộc quá nhiều vào các phương pháp phá hủy như vậy là không bền vững.

Chawla nói rất rõ mục tiêu: “Nhìn vào các khuyết tật trong chất bán dẫn và có thể phát hiện chúng một cách nhanh chóng để giúp ngành công nghiệp là một chủ đề cực kỳ quan trọng. Chúng tôi hy vọng sẽ tăng tốc toàn bộ quy trình bằng cách sử dụng các kỹ thuật chụp ảnh mới và thuật toán nhanh hơn.”

Bước 1: Dùng X‑ray 3D để “quét CT” nguyên con chip

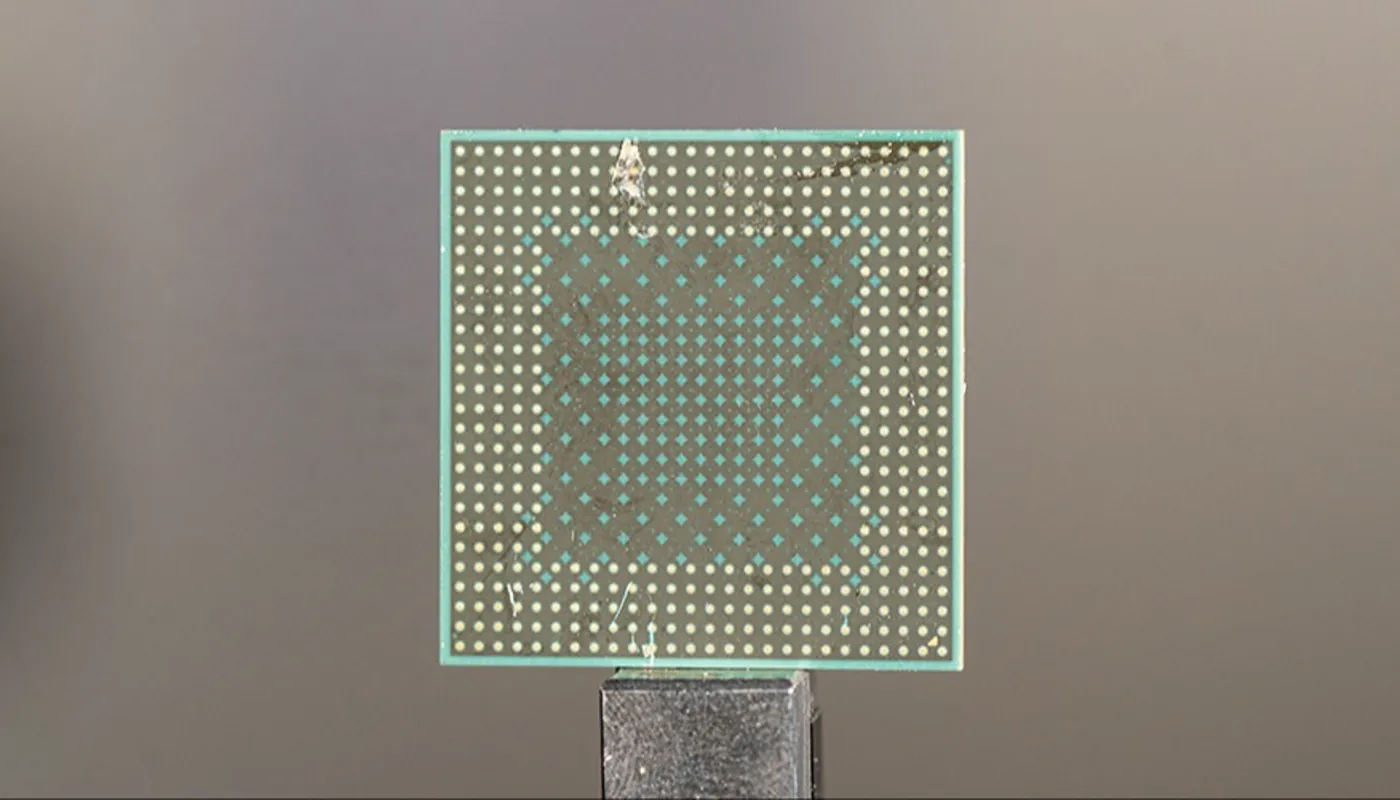

Trung tâm của phương pháp mới là X‑ray imaging và X‑ray tomography – về bản chất, giống như “CT scan” cho chip.

Chawla và nhóm đang làm việc tại:

- Advanced Photon Source (APS) – cơ sở người dùng thuộc Văn phòng Khoa học DOE đặt ở Argonne,

- Đây là nguồn tia X cường độ cao, độ phân giải vượt trội, vốn được dùng cho rất nhiều nghiên cứu vật liệu và cấu trúc.

Mục tiêu ở bước này:

- Tạo ra một bản đồ 3D chi tiết (3D microstructure) của chip và phần đóng gói,

- Nhìn được các cấu trúc và khuyết tật nhỏ nhất có thể – lỗ rỗng, nứt, mất bám, khoảng trống trong hàn, bong tách vật liệu…

- Sau khi xác định được khuyết tật trên ảnh 3D, nhóm lần ngược lại quy trình chế tạo để xem:

- Chúng hình thành ở giai đoạn nào của packaging,

- Có pha nào dễ “đẻ” lỗi hơn (ép khuôn, nối dây, hàn, underfill, đóng nắp…).

Việc hiểu này rất quan trọng, vì packaging hiện đại không còn chỉ là “vỏ ngoài”, mà:

- Chứa liên kết điện và cơ học cực kỳ tinh vi giữa nhiều chip,

- Là nơi có thể xuất hiện lỗi mang tính hệ thống nếu quy trình không tối ưu.

Bước 2: Dùng AI để tự động phát hiện lỗi – không thể mãi ngồi “soi tay”

Nhưng chỉ có X‑ray độ phân giải cao thôi vẫn chưa đủ. Một chip, nếu được quét ở độ phân giải micromét, sẽ tạo ra:

- Lượng dữ liệu khổng lồ,

- Mỗi mẫu là một “núi voxel” 3D,

- Việc con người ngồi soi từng lát cắt là bất khả thi nếu muốn áp dụng ở quy mô công nghiệp.

Đó là lý do bước thứ hai của dự án là trí tuệ nhân tạo:

- Xây dựng các thuật toán để:

- Tự động nhận diện, phân loại khuyết tật trên ảnh 3D,

- Xử lý dữ liệu nhanh,

- Hạn chế tối đa sự can thiệp thủ công.

- Mục tiêu là:

- “Quicker and smarter” – nhanh hơn và thông minh hơn,

- Để quá trình kiểm tra không làm chậm dây chuyền sản xuất.

Nói cách khác, họ muốn biến hệ thống X‑ray + AI thành “con mắt tự động”:

- Liên tục quét và đánh giá tình trạng cấu trúc trong khi chip/packaging đang đi qua các bước xử lý,

- Thông báo sớm nếu có dấu hiệu bất thường,

- Cho phép can thiệp kịp thời để tránh lỗi hàng loạt.

Trong vai trò đồng phát triển thuật toán và xử lý ảnh, Purdue còn có sự tham gia của:

- Charles Bouman – Showalter Professor ngành Điện – Máy tính & Kỹ thuật Y sinh, nổi tiếng trong lĩnh vực xử lý ảnh và reconstruction,

- Greg Buzzard – giáo sư Toán,

- Hany Abdel-Khalik – giáo sư Kỹ thuật Hạt nhân.

Phía Argonne có Francesco de Carlo, đại diện cho đội ngũ chuyên gia X‑ray. Các đối tác khác gồm Erdogan Madenci (Đại học Arizona) và Martin Gall (GlobalFoundries), giúp kết nối với nhu cầu thực tế từ phía công nghiệp bán dẫn.

Bước 3: Không phải lỗi nào cũng “chết người” – phải biết lỗi nào mới đáng sợ

Ngay cả khi bạn có thể phát hiện mọi vết nứt, lỗ rỗng, khuyết tật li ti, một câu hỏi lớn khác xuất hiện: “Cái nào thực sự nguy hiểm cho con chip ngoài đời thật?”

Chawla mô tả đây là phần thứ ba của nghiên cứu:

- Xây cầu nối giữa “lỗi cấu trúc” và “lỗi chức năng”:

- Khuyết tật loại nào sẽ:

- Dẫn đến hỏng hóc sớm,

- Gây lỗi ngắt quãng,

- Hoặc làm tăng nguy cơ bị tấn công (ví dụ do mạch bảo mật hoạt động bất thường)?

- Khuyết tật nào có thể chấp nhận được vì:

- Không ảnh hưởng nhiều đến độ tin cậy,

- Ít tác động đến hiệu năng.

- Khi hiểu rõ mối liên hệ đó, nhà sản xuất có thể:

- Đặt ra ngưỡng chấp nhận thông minh,

- Bắt và loại bỏ đúng những linh kiện sẽ gây hại trong thực tế,

- Thay vì phải “rất bảo thủ” và loại quá nhiều linh kiện chỉ vì thấy một lỗi hình thái nhỏ mà chưa chắc nguy hiểm.

Về lâu dài, dữ liệu từ kỹ thuật này còn có thể:

- Dùng để xây dựng mô hình xác suất hỏng hóc theo thời gian,

- Ước tính khoảng thời gian trước khi một lỗi cụ thể dẫn đến hỏng thiết bị – ví dụ như smartphone, thiết bị IoT.

Lợi thế lớn nhất: Không phá hủy, có thể “chụp CT” nhiều lần trong suốt dây chuyền

Một trong những điểm Chawla nhấn mạnh là tính nondestructive (không phá hủy) của kỹ thuật: “Ngành bán dẫn đã quen với việc lấy một linh kiện lỗi, cắt nó ra, nghiên cứu – rất tốn công và tốn thời gian, hơn nữa là bạn cũng mất luôn linh kiện đó. Với kỹ thuật chụp ảnh không phá hủy, chúng tôi hy vọng có được cách chụp ‘snapshot’ cấu trúc chip trong khi nó đi qua dây chuyền sản xuất, để bạn luôn biết tình trạng của linh kiện.”

Điều này mở ra các kịch bản mới:

- Kiểm tra nhiều lần tại các điểm khác nhau trong quy trình đóng gói,

- Theo dõi sự tiến triển của một khuyết tật – nó phát sinh ở đâu, lớn lên nhanh không,

- Sử dụng dữ liệu đó để:

- Điều chỉnh thông số quy trình,

- Giảm nguy cơ xuất hiện lỗi có hệ thống.

Purdue, Argonne và “mảnh ghép bán dẫn” trong chiến lược Purdue Computes

Dự án của Chawla là một phần trong:

- Chương trình Future of Semiconductors của Quỹ Khoa học Quốc gia (NSF),

- Đồng thời gắn với sáng kiến Purdue Computes – chiến lược của Purdue tập trung vào:

- Nghiên cứu & phát triển bán dẫn,

- Trí tuệ nhân tạo vật lý (physical AI),

- Khoa học máy tính,

- Khoa học & kỹ thuật lượng tử.

Purdue đang cố gắng xây dựng một cụm bán dẫn (semiconductor cluster) tại West Lafayette:

- Bằng đầu tư hạ tầng nghiên cứu,

- Phát triển chương trình đào tạo nhân lực,

- Hợp tác chặt chẽ với các phòng thí nghiệm quốc gia như Argonne,

- Và các công ty như GlobalFoundries.

Nghiên cứu về X‑ray + AI cho phát hiện khuyết tật là một ví dụ điển hình. Nó kết nối:

- Hạ tầng photon năng lượng cao của DOE,

- Chuyên môn xử lý ảnh và vật liệu của Purdue,

- Yêu cầu thực tế của nhà sản xuất chip,

- Dưới cùng một mục tiêu: làm cho thế hệ chip tiếp theo tin cậy hơn, an toàn hơn và rẻ hơn để kiểm tra.

Chawla cho biết ông kỳ vọng kết quả sẽ được công bố ngay từ cuối năm nay, sau khi hoàn tất các thử nghiệm và phân tích.

Kết luận: “Máy quét CT + AI” cho chip – mảnh ghép quan trọng để giữ thế giới số chạy trơn tru

Trong thời đại mọi thứ từ xe hơi, máy bay, bệnh viện đến lò phản ứng hạt nhân đều phụ thuộc vào chip, việc một khuyết tật nhỏ xíu dẫn đến lỗi lớn không còn là chuyện viễn tưởng.

Cách tiếp cận mà Purdue – Argonne đang theo đuổi:

- Dùng X‑ray 3D để nhìn xuyên qua mọi lớp đóng gói,

- Dùng AI để soi và hiểu những gì mắt người không thể xử lý kịp,

- Dùng kiến thức vật liệu để phân biệt lỗi “vô hại” và lỗi “sát thủ”,

Là một bước tiến quan trọng để:

- Giảm phụ thuộc vào các phương pháp kiểm tra phá hủy chậm chạp,

- Nâng cao độ an toàn và độ tin cậy của thế hệ chip tương lai,

- Và về lâu dài, giúp ngành bán dẫn tự tin hơn khi bước vào kỷ nguyên packaging phức tạp, nơi một khuyết tật nhỏ hơn sợi tóc cũng có thể quyết định vận mệnh của cả một hệ thống.